EWICONの製作はとてもゆっくり進んでいます。

一昨年から作り始めたEWICONですが、いろいろ変更したので、ぼちぼち記事をアップしていきます。

- レイテンシーの改善

- ピッチベンド用LPFをPSoC内蔵LPFに変更

- MIDI入出力基盤の製作(実験用)

- VCA基板製作(実験用)

- MIDIパーサーのバグフィックス(Running Status)とSysExの受信サポート

- ブレス感度の調整(アナログ:リニア)

- Modulation実装の仕様確定

- ピン不足対応(I2C LCDへの変更)

- CPU利用率をポートから観察できるようにする

今回の記事では、1と2をまとめました。

やっぱ途中経過も記事にしておかないと、やってる本人が何をやっているのか分からなくなるね・・・

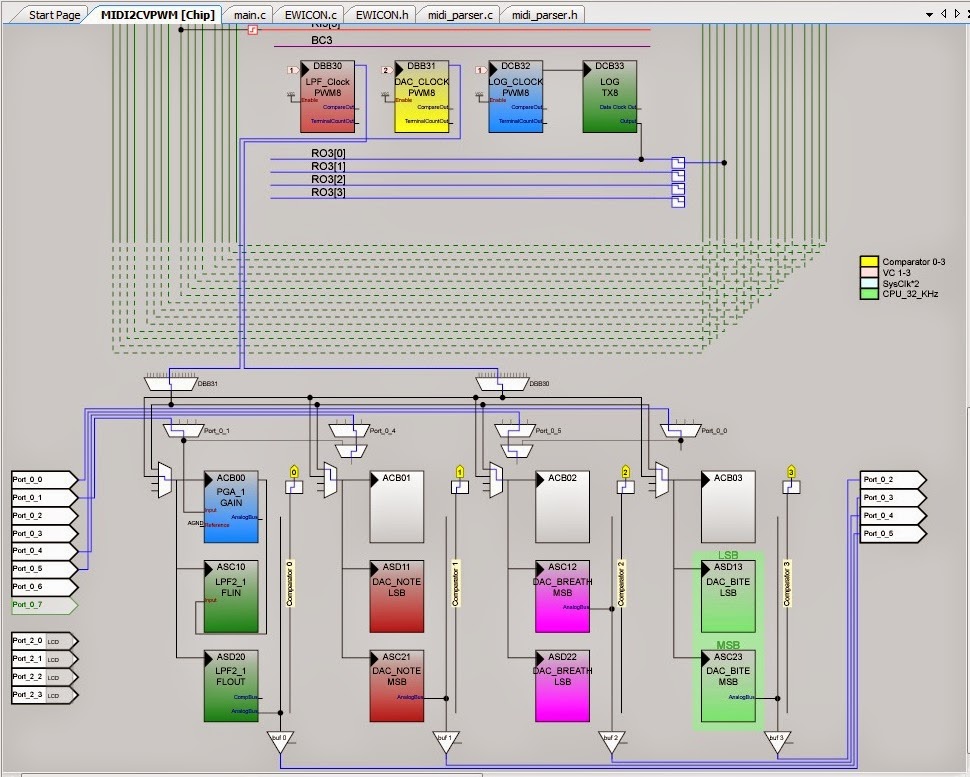

とりあえず、今のところ回路図はこんな感じになっています。まだテスト中なのでどんどん変更が入っていますが・・・

プリント基板制作上の都合もありまして、基板を分けることにしました。

今のところ4分割(アナログ部、デジタル部、電源部、MIDI-IO部)になってます。

| 全体を把握できるようブロック図も作ってみた |

| アナログ部。 まだまだテストが不十分・・・ |

| デジタル部。 PSoC1 で I2CのLCDとかデバッグ用のUARTなど |

1.レイテンシーの改善

前回・前々回の記事でCVのレイテンシと安定性についてコメントしました。

- 「EWICONの作成・・・その1」の「レスポンス(レイテンシー)について」で MIDI受信からCVが安定するまで 2.34ms 掛かっている事。

- 「EWICONの作成・・・その2 」の「PWMからCVを作成する回路・・・ふたたび」でPWMの周波数を高くしてCV電圧を安定させたい。

これらの問題を解決するために、今回は PWM方式をやめ PSoC 内蔵の D/Aコンバーター(DAC) 方式に変更しました。ついでに部品数も少し減らせますね。

PSoC(CY8C29466)では最大で四つのDACが使用できます。そこでビット数の少ないMIDIメッセージ(7ビット) をDAC経由で出力することにしました。

対象メッセージは、ノート、ブレス、バイト(リップセンサー)です。

DACの分解能は6ビット、8ビット、9ビットから選べます。

DACは初めて使用するので調べながらの実装です。

・・・で、とりあえず 8ビットあれば十分なので 8Bit DACを使ってみようと思います。

PSoCのアナログ・ブロックの構成

|

| 右の三列がDAC、ちなみに一番左の列はLPF |

DAC用のクロックの決定

DAC用のクロックはPWM8モジュールで生成し、DACに供給することにします。

しかし、クロック周波数の適正値が分かりません。そこで、片っ端からテストをしながら決めることにしす。

テストをすると言っても、何をどう測定すれな良いのかもわからないので、今回は電源投入時(MIDIデータが流れていない時)のDAC出力ピンの電圧と演奏時(MIDIデータを流した時)の電圧を測定しました。

Period

|

Plus

Width |

Clock Source

(Hz) |

DAC8 Clock

(Hz) | 電源投入時 | 演奏時 | ||||

| 各チャンネルの 電圧(V) | 各チャンネルの ノイズ(mVp-p) | 各チャンネルの 電圧(Vp-p) | |||||||

| Note | Breath | Note | Breath | Note | Breath | ||||

| 1024 | 512 | 5,996,544.00 | 5,856.00 | 0.130 | 0.056 | 240.00 | 160.00 | hang-up | hang-up |

| 512 | 256 | 5,996,544.00 | 11,712.00 | 0.127 | 0.057 | 240.00 | 160.00 | hang-up | hang-up |

| 256 | 128 | 5,996,544.00 | 23,424.00 | 0.129 | 0.055 | 240.00 | 160.00 | 5.120 | 4.720 |

| 128 | 64 | 5,996,544.00 | 46,848.00 | 0.132 | 0.060 | 240.00 | 160.00 | 5.040 | 4.640 |

| 96 | 48 | 5,996,544.00 | 62,464.00 | 0.129 | 0.057 | 240.00 | 160.00 | 5.040 | 4.720 |

| 48 | 24 | 5,996,544.00 | 124,928.00 | 0.132 | 0.060 | 240.00 | 160.00 | 5.040 | 4.640 |

| 32 | 16 | 5,996,544.00 | 187,392.00 | 0.144 | 0.066 | 240.00 | 160.00 | 5.040 | 4.640 |

| 24 | 12 | 5,996,544.00 | 249,856.00 | 0.146 | 0.067 | 240.00 | 160.00 | 5.040 | 4.640 |

| 16 | 8 | 5,996,544.00 | 374,784.00 | 0.150 | 0.075 | 240.00 | 160.00 | 5.040 | 4.640 |

| 12 | 6 | 5,996,544.00 | 499,712.00 | 0.156 | 0.080 | 240.00 | 160.00 | 5.040 | 4.640 |

| 8 | 4 | 5,996,544.00 | 749,568.00 | 0.176 | 0.103 | 320.00 | 320.00 | 5.040 | 4.640 |

| 6 | 3 | 5,996,544.00 | 999,424.00 | 0.215 | 0.300 | 480.00 | 880.00 | 4.640 | 4.640 |

| 4 | 2 | 5,996,544.00 | 1,499,136.00 | 1.399 | 1.293 | 720.00 | 720.00 | 3.360 | 3.280 |

結果、DAC8 Clockが遅い(5,856~11,712Hz)とハングアップ、速すぎると何も処理していない時のピンの電圧が微妙に高くなっていきます。比較的安定していたのは DAC8 Clock が 124,928~749,568Hz の範囲でした。今回は真ん中くらいを取って、ブルーのラインで示したクロック周波数(249,856Hz)にしました。

DAC用の基準電圧の決定

次に決めなければいけないのは基準となる電圧です。DACのプロパティ名で言うと「RefMux」になります。

以下にRefMuxの設定値ごとのテスト結果をまとめておきます。

| Ref Mux 設定値 | Vdd | RefLo | AGND | RefHi | テ ス ト 順 | テスト結果 |

(VDD/2)+/-BandGap

| 3.3 V | 0.35 V | 1.65 V | 2.95 V | ||

| 5.0 V | 1.2 V | 2.5 V | 3.7 V | 4 | ||

(Vdd/2)+/-(Vdd/2)

| 3.3 V | 0.0 V(Vss) | 1.65 V | 3.3 V(Vdd) | ||

| 5.0 V | 0.0 V(Vss) | 2.5 V | 5.0 V(Vdd) | 1 | RefLo および RefHi 付近で電圧が不安定 | |

| BandGap+/-BandGap | 3.0 V ~ 5.0 V | 0.0 V(Vss) | 1.30 V | 2.60 V | ||

| (1.6*BandGap)+/-(1.6*BandGap) | > 4.16 V | 0.0 V(Vss) | 2.08 V | 4.16 V | 2 | RefLo付近の電圧が不安定 |

| (2*BandGap)+/-BandGap | > 3.9 V | 1.3 V | 2.6 V | 3.9 V | 3 | OK --- これを採用する(設計値と実測値の乖離が少なかった) |

| (2*BandGap)+/-P2[6] | 3.0 V ~ 5.0 V | 2.6V-P2[6] | 2.6 V | 2.6V+P2[6] | ||

| P2[4]+/-BandGap | 3.0 V ~ 5.0 V | P2[4]-1.3 V | P2[4] | P2[4]+1.3 V | ||

| P2[4]+/-P2[6] | 3.0 V ~ 5.0 V | P2[4]-P2[6] | P2[4] | P2[4]+P2[6] |

・・・で、BandGap? AGND?

この表の意味がさっぱりわかりません。そこで、またまた片っ端から実機でテストです。

テストは MIDI Note No 0 ~ 127 までを順に演奏し、DACの出力電圧をテスターで測定しました。

テスト結果を、テストした順にまとめておきます。

テスト番号2:(Vdd/2)+/-(Vdd/2)、8Bit DAC、9Bit DAC

RefLo:机上値(0.0V)、実測値(0.07V)

RefHi:机上値(5.0V)、実測値(4.93V)

RefLo付近(Note No 0~3) の電圧が 0.07~0.12V 位で予定していた電圧になっていません。

RefHi付近(Note No 120~127) の電圧が全て 4.930V となり、頭打ちの状態で予定していた電圧になっていません。

なぜ、RefLo、RefHi 付近のみ電圧が不安定なのでしょうか?

RefHi付近(Note No 120~127) の電圧が全て 4.930V となり、頭打ちの状態で予定していた電圧になっていません。

なぜ、RefLo、RefHi 付近のみ電圧が不安定なのでしょうか?

それ以外の電圧はだいたいOKでした。

なんかおかしいので、精度の高い 9Bit DACに変更してテストしてみましたが、結果は同じで、うまくいきませんでした。

テスト番号4:(1.6*BandGap)+/-(1.6*BandGap)、9Bit DAC

RefLo:机上値(0.0V)、実測値(0.0665V)

RefHi:机上値(4.16V)、実測値(4.13V)

RefHi付近は、ほぼ予定通り。

テスト番号5:(2*BandGap)+/-BandGap、8Bit DAC

RefLo:机上値(1.3V)、実測値(1.313V)

RefHi:机上値(3.9V)、実測値(3.877V)

テスト番号1:(VDD/2)+/-BandGap、9Bit DAC

RefLo:机上値(1.2V)、実測値(1.169V)

RefHi:机上値(3.7V)、実測値(3.740V)

|

| Note No 24 ~ 107 は未計測 |

RefLo、RefHi 付近は、ほぼ予定通りです。

なんかここら辺で疲れてきたのすべてのオプションをテストするのはあきらめました。 テスト番号3はテストしていません。

候補として残ったのは、

- テスト番号1:(2*BandGap)+/-BandGap

- テスト番号5:(VDD/2)+/-BandGap

どちらにするかを以下の図を見ながら検討・・・

|

| 『[AN74170] PSoC Designer を使用したPSoC 1 のアナログストラクチャとコンフィグレーション』 P.18 図22 より |

理由は・・・特にありません。

(今のところ予定はないけど、PSoCの電源電圧を3.3Vで動作させる場合を考慮するとテスト番号1 - 『(2*BandGap)+/-BandGap』にしておいた方が良いかも)

あと、途中から 9Bit DACに切り替えてテストしていたのですが、分解能は 8Bitで十分なので 8Bit DACで再度テストし、特に問題なくテスト終了。8Bitで処理が完結するのでバイナリーサイズも若干削減できています。

テスト結果は Google Drive にまとめて保存することにしました。

「EWICON製作メモ」

https://docs.google.com/spreadsheet/ccc?key=0AlvGhZz1HKw6dGxEcmFhM0pGb2tnZVJhTDFqMjhycnc

それと、RefLo、RefHi付近が不安定になる原因について、関連しそうなドキュメントを見つけたのでメモっておく。

『[AN74170] PSoC Designer を使用したPSoC 1 のアナログストラクチャとコンフィグレーション』のP.18 あたりに「リファレンスが電源レールの場合」に説明がある。

・・・でも、今は読んでも良く分からないので宿題としておく。

レイテンシーの測定

前回(PWM使用時)の測定結果。

MIDIデータが確定してからCVが安定するまでの時間は、およそ 2.34ms

今回(DAC使用時)の測定結果

MIDIデータが確定してからCVが確定するまでの時間は、およそ0.28ms。

MIDIデータが確定してからCVが安定するまでの時間は、およそ 2.34ms

|

| CVの立ち上がりが緩やかで遅い |

今回(DAC使用時)の測定結果

MIDIデータが確定してからCVが確定するまでの時間は、およそ0.28ms。

|

| CVの立ち上がりが速い(DACだから当たり前?なのかな) なぜ、前回と同じスケールにしないの? 比べにくいでしょ! |

PWMからDACに変更したことにより、MIDIデータ受信完了からCV発生までの時間が、2.34ms から 0.28ms に短縮されました。

2.ピッチベンド用LPFをPSoC内蔵LPFに変更

ピッチベンドは、分解能の高いMIDIデータ(14ビット)なので以前と同様PWMのままとします。今までは外付けのCRで作ったLPFを使用していましたが、これをPSoCのアナログ・ブロックにLPFをセットする方式に変更しました。PWMの出力を直接アナログ・ブロックに接続することはできないので、出力ポート(Port0[1])経由で結線します。とは言ってもPSoC内で結線できますので、プリント基板上で物理的に接続する必要はありません。

|

| 赤い線のようにPort0[1]からPGA_1に入力。 PGAのゲインは1 |

LPFはLPF2VAを選択。

フィルターの設定はウィザードで・・・

- "Filter Type" : Butterworth

- "F corner" : 140Hz

- "F sample" : 120,000Hz

- "Gain" : 0.0dB

・・・としました。

なぜ、この値にしたかというと・・・

こうやったら上手くいったから。

う~、残念ながら、まだ設計方法がわからないのです。

また、LPFのクロックはPWM8(LPF_Clock)を配置しPeriodに 50(赤線で示した Devide by n の数値)を設定します。そしてLPFの出力はアナログポート(Port0[3])に出力します。

これで、ピッチベンド用PWMの出力ポート(Port0[1])を経由しLPFを通ってアナログポート(Port0[3])から出力されます。

実際にテストした結果は以下にまとめました。

「EWCON製作メモ」の「Pitch Bend(内蔵LPF版)」タブにあります。出力電圧は 0.073V~4.752V で最小値と最大値付近の数データ以外は、ほぼ思った通りの結果となっています。

https://docs.google.com/spreadsheet/ccc?key=0AlvGhZz1HKw6dGxEcmFhM0pGb2tnZVJhTDFqMjhycnc

最小値と最大値付近のデータが不安定ですが、演奏してみるとほとんど気になりませんでした。

ピッチベンドなのでこの程度であれば問題ないかもしれませんが、なぜ最小値と最大値付近の数データだけ不安定なんだろう・・・?

む~、今のところ解決の糸口はまったくつかめていません。

過去記事を読み返しながら書いているのですが、EWICONの制作開始は2012年9月で、ついに三年目に突入か・・・なかなか進まないね~。

EWICONの後にはEWICON専用アナログ音源を作る予定なのに・・・

それにしても記事一覧が欲しい。過去記事を探すのが面倒になってきた。

では・・・

0 件のコメント:

コメントを投稿